# Leadframe Design Enhancement for Die Attach Improvement

## Rennier Rodriguez, Edwin Graycochea Jr., Frederick Ray Gomez

New Product Development & Introduction, Back-End Manufacturing & Technology, STMicroelectronics, Inc. Calamba City, Laguna, Philippines 4027

**Abstract**— Design modification is one of the alternative approach to adjust the standard of a certain configuration into a specified limit or to provide a potential solution to incapability of the current situation. This paper presents a leadframe carrier design incorporated with a stand-off structure that will maintain a consistent bond line thickness criteria for quad flat no-lead (QFN) assembly and similar application. Manufacturing simplification is the primary goal of the modification with secondary matrix of reliability and quality improvement as well. The fabrication method and insights from the authors are also discussed.

Keywords—Bond line thickness; leadframe; design improvement; die attach process.

#### I. INTRODUCTION

Die attach is one of the key process for integrated circuit (IC) assembly responsible in picking and bonding of silicon die from the wafer to a carrier or substrate. This process also deals with conductive and non-conductive paste same as with die attach films (DAF) application to establish adhesion between die and carrier. To ensure its integrity during production, die attach is bounded by multiple criteria such as placement tolerances, silicon die bonding condition, visual inspection criteria and the correct height and volume of the semiconductor epoxy to be applied between silicon die and leadframe.

Quality as defined by G. Taguchi explains that any variation from the target may incur dissatisfaction. On manufacturing translation, controlling the variation and having the capability to maintain the distribution of responses close to the defined target criteria significantly improves the quality of a product. But on the other hand, as the responses are moving closer to the maximum or minimum acceptable limit or away from the target, the corresponding quality is starting to degrade also.

Bond line thickness (BLT) is the term used to identify the height of the epoxy between silicon die and pad after bonding process. BLT is one of the response in die attach process that is difficult to predict and stabilize during assembly. Factors like environment, temperature, glue work life, formulation has a direct effect on certain characteristic of glue such as open time, thixo-index, viscosity which is the primary ingredient for consistency and repeatability of epoxy glues. Since there is large variation in the primary input of die attach, maintaining a consistent and predictable process is a challenging process to start with.

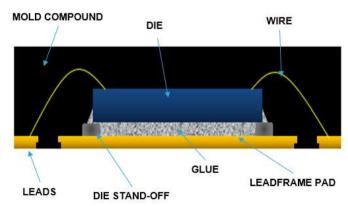

Fig. 1. Package cross-section showing BLT.

A modification in the leadframe design that is presented in this paper discusses an innovative idea that enables improvement for consistent BLT. The method, design and inputs from the author is included also on the succeeding slides.

### II. DESIGN AND POCESS SOLUTION

Quad flat no-lead (QFN) device is composed of silicon die bonded to a leadframe pad where the active circuit of the die is connected to the lead and the overall unit is encapsulated by a molding compound. The leadframe used in the conventional design of QFN is a flat sheet of copper or plated copper material. Fig. 2 shows the cross sectional view of the modified leadframe design wherein there is an embossed portion which is located at every corner of the die. The modified design or stand-off has a height equivalent to the required BLT thickness. During die bonding sequence, the force applied by the bondhead will press the silicon die until the defined height of the stand-off is reached. In this scenario, the stand-off acts as a "stopper" for the die silicon die.

Fig. 2. Package cross-section showing stand-off design.

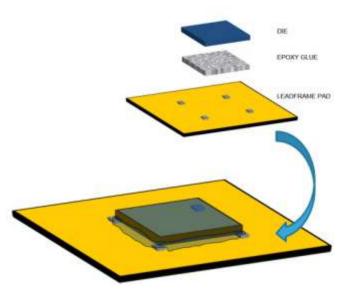

Dispensing process for stand-off design is explained in Fig. 3. This can be realized through normal dispensing process or stencil printing process. A conductive or non-conductive can be used for adhesion. Machine model is not restricted by the stand-off design.

Fig. 3. Dispense process.

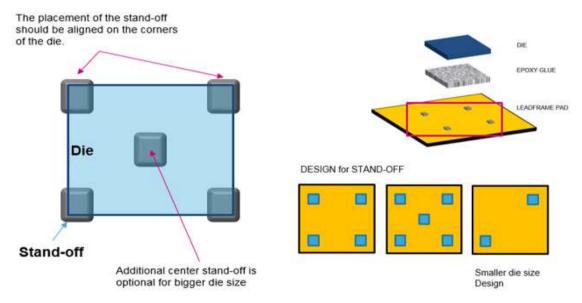

Stand-off design for wide range of silicon die sizes is explained in Fig. 4. Different stand-off design is applicable for certain size of die sizes. For smaller die, 2 stand-off components are enough to hold the unit. Four (4) or more stand-off design on the pad caters medium to large size of the die. A stand-off on the middle portion is recommended to generate additional support at the middle portion during die bonding.

Fig. 4. Stand-off design options for leadframe package.

### III. CONCLUSION

Realization of this modified design on leadframe contributes to process simplification of QFN package or similar technology. Process capability improvement is the primary objective of the design through consistent BLT height bonding using semiconductor glues. Productivity and reliability can be significantly improved as well as a result of capability improvement since BLT is a critical characteristic for integrated circuit assembly.

### ACKNOWLEDGMENT

The authors would like to thank the New Product Development & Introduction (NPD-I) team and the Management Team for the countless support.