# Large-Signal Analysis of a 1V Common-Gate with Common-Source Active Balun Circuit

Frederick Ray I. Gomez<sup>1,2</sup>, Maria Theresa G. De Leon<sup>2</sup>, John Richard E. Hizon<sup>2</sup> <sup>1</sup>New Product Development & Introduction Department, STMicroelectronics, Inc., Calamba City, Laguna, Philippines 4027 <sup>2</sup>Microelectronics and Microprocessors Laboratory, University of the Philippines, Diliman, Quezon City, Philippines 1101

Keywords— Active balun; large-signal analysis; common-gate with common source active balun; saturation region.

## I. OVERVIEW

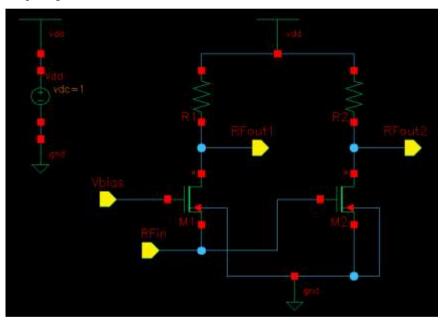

An active balun (balanced-unbalanced) circuit is a type of transformer that converts signals that are single-ended or unbalanced with respect to ground into signals that are differential or balanced with respect to ground. Fig. 1 illustrates an active balun topology comprising of 2 amplifiers namely common-gate amplifier (M1) and the common-source amplifier (M2). The input signal is fed into the drain node or terminal of M1 and into the gate node of M2, while the outputs are probed at the drain terminals of M1 and M2. Load resistors R1 and R2 dictate the output voltages as well as the voltage gains of the two output signals with respect to the input signal.

Fig. 1. Common-gate with common-source active balun circuit schematic.

Common-source topology exhibits a relatively high input impedance while providing voltage gain and requiring a minimal voltage headroom. With this, it finds wide applications in analog circuits and its frequency response is of interest. Common-gate topology exhibits no Miller multiplication of capacitances, potentially achieving a wide band [1-2]. However, the low input impedance may load the preceding stage. Furthermore, since the voltage drop across R1 is typically maximized to obtain the required gain, the direct current (DC) level of the input signal must be quite low. With the two topologies cascaded to function as an active balun, one major challenge would be to generate balanced gain for the two outputs RFout1 and RFout2 with respect to the input signal RFin, given that the input signal is fed into two different transistor ports.

## II. LARGE-SIGNAL ANALYSIS

Direct current (DC) analysis or large-signal analysis is critical in the design of the active balun circuit as it determines the optimum operating point and bias conditions. Moreover, large-signal values are crucial to define the small-signal parameters. On the other hand, small-signal parameters are important to determine the frequency response of the circuit like the maximum frequency of operation and the effective bandwidth, and ensuring that the designed active balun would produce the target gain or attenuation at the desired frequency of operation.

To achieve the maximum output swing for M2, VRFout2 (or simply V2) should be between supply voltage ( $V_{DD}$ ) and the

Volume 3, Issue 8, pp. 77-79, 2019.

saturation voltage ( $V_{DSAT}$ ) or the overdrive voltage ( $V_{OV}$ ) of the transistor, ensuring also that the transistor operates at the saturation region. With  $V_{DD} = 1V$ , and  $V_{OV}$  set to 200mV, the output at RFout2 could swing from 0.2V to 1V. With the said output swing range, output DC voltage (or bias voltage) V2 is therefore computed as

$$V_{DD} > V2 \ge V_{DSAT2} \qquad \rightarrow \qquad 1V > V2 \ge 0.2V \tag{1}$$

$$V2 = V_{RFout2} = \frac{V_{DD} + V_{OV2}}{2} = \frac{1V + 0.2V}{2} = 0.6V$$

(2)

Input bias voltage (VRFin or simply  $V_{IN}$ ) is the same as the gate voltage ( $V_{G2}$ ) of M2 and the source voltage ( $V_{S1}$ ) of M1. To satisfy the condition  $V_{DS2} \ge V_{DSAT2} = V_{OV}$ , input voltage ( $V_{IN}$ ) should be properly set. With threshold voltage ( $V_t$ ) set to 400mV,

$$V_{DS2} = V_{GS2} - V_t \ge V_{DSAT2} \rightarrow (V_{IN} - 0) - 0.4V = 0.2V$$

(3)

$$V_{IN} = 0.6V$$

(4)

With  $V_{IN}$  as the source voltage ( $V_{S1}$ ) of transistor M1, output DC voltage for RFout1 which is V1 (or VRFout1) could be calculated for maximum output swing.

$$V_{DD} > V1 \ge V_{IN} \qquad \rightarrow \qquad 1V > V1 \ge 0.6V \tag{5}$$

$$V1 = V_{RFout1} = \frac{V_{DD} + V_{IN}}{2} = \frac{1V + 0.6V}{2} = 0.8V$$

(6)

Maximum output swing could be achieved at output DC voltage V1 set to 0.8V and at V2 set to 0.6V. To compute for the proper biasing of transistor M2, with input voltage kept at minimum allowed which is at 0.6V,

$$V_{DS1} = V_{GS1} - V_t \ge V_{DSAT1} \rightarrow (V_{BIAS} - V_{IN}) - 0.4V = 0.2V$$

(7)

$$V_{BIAS} = 1.2V \tag{8}$$

If overdrive voltage ( $V_{OV}$ ) is set to 100mV for both transistors M1 and M2, output swings for V1 and V2 could be adjusted. Also, input voltage ( $V_{IN}$ ) and bias voltage ( $V_{BIAS}$ ) for M2 could be lowered. Recalculations are shown in the succeeding expressions.

$$V2 = \frac{V_{DD} + V_{0V2}}{2} = \frac{1V + 0.1V}{2} = 0.55V$$

(9)

$$V_{IN} = 0.4V + 0.1V = 0.5V \tag{10}$$

$$V1 = \frac{V_{DD} + V_{IN}}{2} = \frac{1V + 0.5V}{2} = 0.75V$$

(11)

$$V_{BIAS} = V_{IN} + 0.4V + 0.1V = 1V$$

(12)

With input DC voltage ( $V_{IN}$ ) set to 0.5V, amplifier efficiency in terms of gmoverId could be derived for the two branches or outputs.

$$g_{m1} = \frac{\delta I_{DS1}}{\delta V_{GS1}} = \mu C_{ox} \frac{W_1}{L_1} (V_{GS1} - V_t) (1 + \lambda V_{DS1})$$

(13)

$$g_{m2} = \frac{\delta I_{DS2}}{\delta V_{GS2}} = \mu C_{ox} \frac{W_2}{L_2} (V_{GS2} - V_t) (1 + \lambda V_{DS2})$$

(14)

Substituting the expression for the drain current or drain-to-source current ( $I_{DS}$ ) into the tansconductance ( $g_m$ ),

$$g_{m1} = \frac{\delta I_{DS1}}{\delta V_{GS1}} = \frac{2I_{DS1}}{V_{GS1} - V_t} = \frac{2I_{DS1}}{V_{BIAS} - V_{IN} - V_t}$$

(15)

$$\frac{g_{m1}}{I_{DS1}} = \frac{2}{V_{BIAS} - V_{IN} - V_t} = gmoverId1$$

(16)

http://ijses.com/ All rights reserved

Volume 3, Issue 8, pp. 77-79, 2019.

$$g_{m2} = \frac{\delta I_{DS2}}{\delta V_{GS2}} = \frac{2I_{DS2}}{V_{GS2} - V_t} = \frac{2I_{DS2}}{V_{IN} - V_t}$$

(17)

$$\frac{g_{m2}}{I_{DS2}} = \frac{2}{V_{IN} - V_t} = gmoverId2$$

(18)

For low power design, higher gmoverId is recommended. To achieve such,  $V_{IN}$  and  $V_{BIAS}$  should be optimized. With bias voltage ( $V_{BIAS}$ ) fixed, increasing the input voltage ( $V_{IN}$ ) increases the efficiency of M1 in terms of gmoverId1. On the other hand, increasing  $V_{IN}$  would decrease the efficiency of M2 in terms of gmoverId1. Lowering the drain current or supply current ( $I_{DS}$ ) would also mean lowering  $g_m$  to maintain the efficiency for low power consumption. With this, there is a limit in the efficacy of optimizing the input voltage ( $V_{IN}$ ), bias voltage ( $V_{BIAS}$ ) and supply current ( $I_{DS}$ ) to maximize the efficiency in terms of gmoverId.

As previously assumed,  $V_{OV}$  is set to 100mV for minimum attenuation and/or maximum voltage swing in outputs RFout1 and RFout2 with respect to the input RFin.

Transistor dimensions, particularly the transistor gate widths W1 and W2 of M1 and M2, respectively, could be approximated with values inputted in the square-law model in (19) and (20), respectively.

$$I_{DS1} = \frac{\mu C_{ox}}{2} \frac{W1}{L} \left[ (V_{BIAS} - V_{IN}) - V_t \right]^2 \left[ 1 + \lambda (V1 - V_{IN}) \right]$$

(19)

$$I_{DS2} = \frac{\mu C_{ox}}{2} \frac{W2}{L} (V_{IN} - V_t)^2 (1 + \lambda \cdot V2)$$

(20)

Drain current  $(I_{DS})$  dictates the transistor gate width (W). Increasing the supply current will require larger transistor width. As mentioned in the earlier section, larger W would result to a larger transistor gate area which in turn increases the parasitic capacitances. Thus design tradeoff for supply current  $(I_{DS})$  and transistor sizing is inevitable.

#### ACKNOWLEDGMENT

The authors would like to acknowledge the valuable support of the Department of Science and Technology (DOST), DOST-PCASTRD, DOST-ERDT, and the Microelectronics and Microprocessors Laboratory (Microlab) of the University of the Philippines. Author F.R. Gomez is thankful to the STMicroelectronics Calamba New Product Development & Introduction (NPD-I) team and the Management Team for the usual great support.

#### REFERENCES

- [1] B. Razavi, Design of Analog CMOS Integrated Circuits, New York: McGraw-Hill, 2001.

- [2] P.R. Gray, P.J. Hurst, S.H. Lewis, and R.J. Meyer, Analysis and Design of Analog Integrated Circuits, 4th ed., New York: John Wiley & Sons, Inc., 2001.

- [3] C. Bowick, RF Circuit Design, 1st ed., USA: Howard W. Sams & Co. Inc., 1982.

- [4] F.R. Gomez, M.T. De Leon, and J.R. Hizon, Design of common-gate with common-source active balun for WiMAX receiver front-end, Journal of Engineering Research and Reports, vol. 6, no. 1, pp. 1-9, July 2019.

- [5] F.R. Gomez, M.T. De Leon, and J.R. Hizon, Common-gate with common-source active balun circuit small-signal analysis in CMOS technology, International Journal of Scientific Engineering and Science, vol. 3, no. 8, pp. 19-22, August 2019.

- [6] Cadence Design Systems, Inc. Custom IC / analog / RF design circuit design. https://www.cadence.com/content/cadence-www/global/en\_US/home/tools/ custom-ic-analog-rf-design/circuit-design.html

- [7] F.R. Gomez, M.T. De Leon, and C.R. Roque, Active balun circuits for WiMAX receiver front-end, TENCON 2010 IEEE Region 10 Conference, pp. 1156-1161, November 2010.

- [8] Cadence, LNA design using SpectreRF, Application Note, product version 6.0, November 2005.