# Analysis on Total Harmonic Distortion of CMOS Common-Gate with Common-Source Active Balun Circuit

# Frederick Ray I. Gomez<sup>1,2</sup>, John Richard E. Hizon<sup>2</sup>

<sup>1</sup>New Product Development & Introduction Department, STMicroelectronics, Inc., Calamba City, Laguna, Philippines 4027 <sup>2</sup>Microelectronics and Microprocessors Laboratory, University of the Philippines, Diliman, Quezon City, Philippines 1101

Keywords— Active balun; harmonic distortion; THD; common-gate; common-source; CMOS; efficiency.

### I. CIRCUIT OVERVIEW

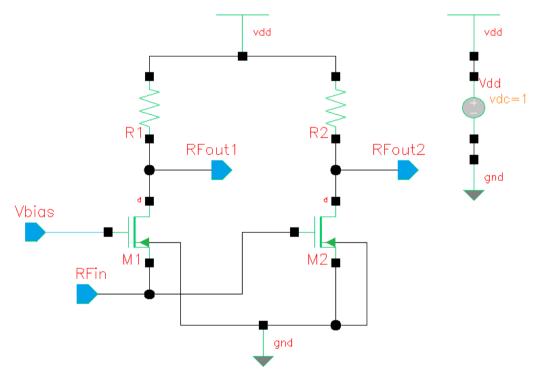

This active balun is comprised of 2 amplifiers namely common-gate amplifier (with transistor M1) in the 1st stage and common-source amplifier (with transistor M2) in the 2nd stage as shown in the Fig. 1. The input signal is fed into the drain of M1 and into the gate of M2, while the outputs are probed at the drains of M1 and M2. Load resistors R1 and R2 indicate the output voltages as well as the voltage gains of the two output signals with respect to the input signal.

Fig. 1. Common-gate with common-source active balun circuit schematic.

Common-source topology exhibits a relatively high input impedance while providing voltage gain and requiring a minimal voltage headroom. With this, it finds wide applications in analog circuits and its frequency response is of interest. Common-gate topology exhibits no Miller multiplication of capacitances, potentially achieving a wide band [1]. However, the low input impedance may load the preceding stage. Furthermore, since the voltage drop across R1 is typically maximized to obtain the required gain, the DC level of the input signal must be quite low. With the two topologies cascaded to function as an active balun, one major challenge would be to generate balanced gain for the two outputs RFout1 and RFout2 with respect to the input signal RFin, given that the input signal is fed into two different transistor ports.

# II. TOTAL HARMONIC DISTORTION

A critical parameter that should also be considered in the design of common-gate with common-source active balun implemented in a complementary metal-oxide semiconductor (CMOS) technology is the total harmonic distortion (THD). THD,

which is also a linearity parameter, is the percentage of the inherent harmonics with respect to the fundamental signal. Ideally, THD is zero, but since this is not really the case for transistors and transistor amplifiers, THD should then be minimized.

For a general starting equation, total input voltage  $(V_{in})$  is assumed to be the sum of direct current (DC) input  $V_{IN}$  and alternating current (AC) input  $v_{in}$ , as a function of time. AC input  $v_{in}$  could be further expressed as vrfcos $\omega$ t, where vrf is the peak value of  $v_{in}$ .

$$Vin(t) = V_{DC} + V_{AC} = V_{IN} + v_{in} = V_{IN} + vrf\cos\omega t \tag{1}$$

For RFout1, total drain current (Ids) is expressed as

$$I_{ds1}(t) = \frac{\beta}{2} [V_{GS} - V_t]^2 = \frac{\beta}{2} \{ [V_{BIAS} - (V_{IN} + v_{in})] - V_t \}^2$$

(2)

$$I_{ds1}(t) = \frac{\beta}{2} \left[ \left( V_{y1}^2 + \frac{vrf^2}{2} \right) - 2V_{y1}vrf \cdot \cos \omega t + \frac{vrf^2}{2} \cdot \cos 2\omega t \right] \tag{3}$$

with

$$V_{y1} = V_{BIAS} - V_{IN} - V_t$$

,  $v_{in} = vrf \cos \omega t$ ,  $\beta = \mu C_{ox} \frac{W}{L}$  (4)

The drain current has three terms, and substituting back the expression for Vy1, the terms are given as

$$I_{0f1} = \frac{\beta}{2} \left[ (V_{BIAS} - V_{IN} - V_t)^2 + \frac{vrf^2}{2} \right] = I_{DC} \rightarrow \text{DC term}$$

(5)

$$I_{1f1} = \frac{\beta}{2} \left[ 2vrf(V_{IN} + V_t - V_{BIAS}) \right]$$

Amplitude of 1st harmonic (6)

$$I_{2f1} = \frac{\beta}{2} \left( \frac{vrf^2}{2} \right)$$

$\rightarrow$  Amplitude of 2nd harmonic (7)

THD of the RFout1 which is the common-gate stage of the active balun, could now be determined.

$$THD_1 = \frac{vrf}{-4[(V_{RIAS} - V_{IN}) - V_t]} = -\frac{vrf}{4V_{OV}} = -\frac{vrf}{8} \frac{g_{m1}}{I_{DS1}}$$

(8)

Minimizing the overdrive voltage  $(V_{OV})$  of transistor M1 would result to higher THD. And increasing the efficiency in terms of gmoverId would also result to higher THD. With this, there is a limit in the effectiveness of optimizing  $V_{OV}$  and gmoverId to minimize the total harmonic distortion.

Now for the RFout2, which is that of the common-source stage, total drain current is expressed as

$$I_{ds2}(t) = \frac{\beta}{2} [V_{GS} - V_t]^2 = \frac{\beta}{2} \{ [(V_{IN} + v_{in}) - 0] - V_t \}^2$$

(9)

$$I_{ds2}(t) = \frac{\beta}{2} \left[ \left( V_{y2}^2 + \frac{vrf^2}{2} \right) + 2V_{y2}vrf \cdot \cos \omega t + \frac{vrf^2}{2} \cdot \cos 2\omega t \right]$$

(10)

with

$$V_{y2} = V_{IN} - V_t$$

and  $v_{in} = vrf \cos \omega t$  (11)

The drain current has three terms, given as

$$I_{0f2} = \frac{\beta}{2} \left[ (V_{IN} - V_t)^2 + \frac{vrf^2}{2} \right] = I_{DC} \rightarrow \text{DC term}$$

(12)

$$I_{1f2} = \frac{\beta}{2} \left[ 2vrf(V_{IN} - V_t) \right] \qquad \rightarrow \qquad \text{Amplitude of 1st harmonic}$$

(13)

$$I_{2f2} = \frac{\beta}{2} \left( \frac{vrf^2}{2} \right)$$

$\rightarrow$  Amplitude of 2nd harmonic (14)

Volume 3, Issue 9, pp. 7-9, 2019.

Total harmonic distortion of the RFout2 which is the common-source stage of the active balun, could now be generated.

$$THD_2 = \frac{vrf}{4(V_{IN} - V_t)} = \frac{vrf}{4(V_{GS2} - V_t)} = \frac{vrf}{4V_{OV}} = \frac{vrf}{8} \frac{g_{m2}}{I_{DS2}} \tag{15}$$

It can be observed that minimizing the overdrive voltage  $(V_{OV})$  of transistor M2 would result to higher THD. Increasing the efficiency in terms of gmoverId would also result to higher THD. With this, there is a limit in the effectiveness of optimizing  $V_{OV}$  and the efficiency gmoverId to minimize the distortion.

### ACKNOWLEDGMENT

The authors would like to thank the Microelectronics and Microprocessors Laboratory team of the University of the Philippines especially to Prof. Maria Theresa De Leon, Ph.D. for the technical support during the course of the study. F.R. Gomez would like to express gratitude to the STMicroelectronics Calamba New Product Development & Introduction (NPD-I) colleagues and the Management Team for the immeasurable support.

## REFERENCES

- [1] B. Razavi, Design of Analog CMOS Integrated Circuits, New York: McGraw-Hill, 2001.

- [2] P.R. Gray, P.J. Hurst, S.H. Lewis, and R.J. Meyer, Analysis and Design of Analog Integrated Circuits, 4th ed., New York: John Wiley & Sons, Inc., 2001.

- [3] W. Sansen, "Distortion in elementary transistor circuits," IEEE Transactions on Circuits and Systems–II: Analog and Digital Signal Processing, vol. 46, no. 3, pp. 315-325, March 1999.

- [4] C. Bowick, RF Circuit Design, 1st ed., USA: Howard W. Sams & Co. Inc., 1982.

- [5] J.R. Hizon and E. Rodriguez-Villegas, "Design tradeoffs in a triode transconductor for low voltage zero-IF channel select filters," 52nd IEEE International Midwest Symposium on Circuits and Systems, September 2009.

- [6] F.R. Gomez, Electronic noise and noise analysis, UP EE 220 Analog IC Design Course, February 2008.

- [7] F.R. Gomez, M.T. De Leon, and J.R. Hizon, Design of common-gate with common-source active balun for WiMAX receiver front-end, Journal of Engineering Research and Reports, vol. 6, no. 1, pp. 1-9, July 2019.

- [8] Cadence, LNA design using SpectreRF, Application Note, product version 6.0, November 2005.

- [9] F.R. Gomez, M.T. De Leon, and C.R. Roque, Active balun circuits for WiMAX receiver front-end, TENCON 2010 IEEE Region 10 Conference, pp. 1156-1161, November 2010.

- [10] Cadence Design Systems, Inc. Custom IC / analog / RF design circuit design. https://www.cadence.com/content/cadence-www/global/en\_US/home/tools/custom-ic-analog-rf-design/circuit-design.html